Category:Phase-locked loops

跳转到导航

跳转到搜索

Deutsch: Kategorie:Phasenregelschleifen (PLL).

English: Category:phase-locked loops.

Français : Catégorie:boucles à phase asservie.

Nederlands: Categorie:fasevergrendelingslussen (PLL-schakelingen)..

electronic circuit | |||||

| 上传媒体 | |||||

| 上级分类 | |||||

|---|---|---|---|---|---|

| 可分為 |

| ||||

| |||||

分类“Phase-locked loops”中的媒体文件

以下200个文件属于本分类,共220个文件。

(上一页)(下一页)-

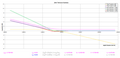

1 - 1 tolerance with different G.png 1,073 × 452;33 KB

-

100 percent frequency uncertainty.pdf 1,747 × 1,164;11 KB

-

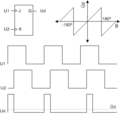

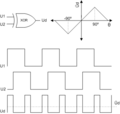

101010 Ph Comp Characteristic.png 1,046 × 360;42 KB

-

1st n 2nd contrasted at trans disapp.png 1,105 × 475;28 KB

-

1st n 2nd jitter transfer ie noise rejection.png 752 × 508;51 KB

-

1st order loop - pulse response.png 939 × 459;19 KB

-

1st order type 0 slave CDR architecture.png 901 × 389;25 KB

-

1st order type 1 loop.pdf 1,754 × 843;45 KB

-

1st order type 1 loop.png 1,094 × 754;56 KB

-

2 - 1 tolerance.png 1,062 × 455;32 KB

-

2 - 2 and 2 - 1 Application for the De-jitterizer.png 1,169 × 604;153 KB

-

2.1 Loop . Filter reference to simulate.png 957 × 304;16 KB

-

2.1 Loop block diagram to simulate.png 1,111 × 569;43 KB

-

2.2 Loop . Alternative Filter reference to model n simulate.png 1,123 × 731;52 KB

-

2.2 Loop . Filter reference to simulate.png 958 × 303;16 KB

-

2.2 Loop block diagram to simulate.png 1,097 × 556;43 KB

-

2013 10 25 1-1 b.b. slew rate for BW.pdf 1,754 × 814;69 KB

-

2014 10 12 Slew rate limited 1-1 PLL.png 3,237 × 1,367;363 KB

-

2014 10 27 CDR phase tolerance range vs jitter frequency 2- 2.pdf 1,754 × 1,239;505 KB

-

2014 10 27 VCO frequency range vs jitter frequency 2- 2.pdf 1,754 × 1,239;38 KB

-

2014 10 28 CDR phase tolerance range vs jitter frequency 2- 2.png 1,788 × 1,259;285 KB

-

2014 2 26 PDs n PFD free running waveforms.pdf 1,579 × 679;668 KB

-

2014 4 27 Waveforms in a 2-2 CDR.png 1,380 × 856;267 KB

-

2014 5 15 Sinusoid properties.png 742 × 601;38 KB

-

2015 1 1 onset of triangular SR in 2.2.pdf 1,754 × 914;73 KB

-

2015 12 20 6 Single pole filter for 2-1 CDR.pdf 1,487 × 1,087;42 KB

-

2015 2 14 Jitter transfer bandwidths.pdf 1,770 × 1,010;45 KB

-

2015 3 11 Approx 1 + 2.svg 918 × 241;190 KB

-

2015 3 11 Approx 3 + 4.svg 920 × 233;191 KB

-

2015 3 11 Approx 5 + 6.svg 919 × 224;192 KB

-

2015 3 15 Approx 7 + 8.svg 902 × 189;186 KB

-

2015 3 21 Approx 1 + 2.pdf 1,650 × 447;84 KB

-

2015 3 22 Approx 3 + 4.pdf 1,650 × 443;126 KB

-

2015 3 22 Approx 5 + 6.pdf 1,650 × 420;115 KB

-

2015 3 22 Approx 7 + 8.pdf 1,650 × 435;120 KB

-

2015 3 25 Approx 1 + 2.svg 705 × 177;180 KB

-

2015 3 25 Approx 3 + 4.svg 758 × 167;237 KB

-

2015 3 25 Approx 5 + 6.svg 758 × 149;226 KB

-

2015 3 25 Approx 7 + 8.svg 815 × 170;229 KB

-

2015 4 1 Dejitter via phase al.svg 602 × 439;217 KB

-

2016 1 12 tolerance and modulation index 1 - 1 bbang.png 1,565 × 1,205;175 KB

-

2016 1 12 tolerance and modulation index 2 - 1 linear.png 1,565 × 1,205;173 KB

-

2016 1 12 tolerance and modulation index 2 - 2 bbang.png 1,532 × 1,179;207 KB

-

2016 3 5 DeJitterizer with parallel processing.png 673 × 496;76 KB

-

2106 3 7 De-jitterizer (full speed clocks).png 1,148 × 524;126 KB

-

2nd order type 1 loop, 3 examples.pdf 1,754 × 1,239;59 KB

-

2nd order type 2 linear model with jitter transfer equation.png 749 × 431;27 KB

-

2nd order type 2 loop, 3 examples.pdf 1,754 × 1,239;59 KB

-

3 loops go free running.png 1,010 × 360;31 KB

-

Acquisition 1st order.png 1,065 × 420;33 KB

-

Acquisition after some slips back and forth total lock delay 2 pi.png 1,059 × 411;61 KB

-

Acquisition and tracking of the bang bang 1 -1 loop.png 994 × 504;72 KB

-

Acquisition of a 2-2 with bang-bang PFD.pdf 1,754 × 1,239;116 KB

-

Acquisition of the bang bang 1 -1 loop density 100%.pdf 1,670 × 739;61 KB

-

Acquisition of the bang bang 1 -1 loop density 50%.pdf 1,668 × 727;58 KB

-

Acquisition of the bang bang 1 -1 loop Fig 2.png 994 × 511;68 KB

-

Acquisition of the bang bang 1 -1 loop tol lim.pdf 1,754 × 814;70 KB

-

Acquisition of the bang bang 1 -1 loop, transition density 100%.png 1,385 × 583;113 KB

-

Acquisition of the bang bang 1 -1 loop, transition density 50%.png 1,385 × 583;103 KB

-

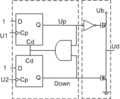

All Degital PLL (block diagram-2).PNG 1,080 × 700;66 KB

-

All Digital PLL (block diagram).PNG 960 × 400;35 KB

-

All Digital PLL (DCO).PNG 440 × 640;26 KB

-

All Digital PLL (MOS Varactor characteristic).PNG 760 × 700;53 KB

-

All Digital PLL (TDC timing-chart).PNG 750 × 710;43 KB

-

All Digital PLL (TDC).PNG 1,000 × 680;48 KB

-

An example of elastic buffer.svg 394 × 234;45 KB

-

Analog PLL (block diagram).PNG 960 × 400;32 KB

-

Bang bang Phase Detector with “hold”.jpg 1,489 × 861;206 KB

-

Bang – Bang Phase Detector.png 929 × 456;26 KB

-

Bang-bang PFD acquisition.png 1,390 × 830;189 KB

-

Bang-bang PFD waveforms constant Df random input.png 1,385 × 584;87 KB

-

Bang-bang PFD waveforms constantDf 101010 input.png 1,385 × 653;84 KB

-

Bang-bang PFD with constant input difference.png 1,385 × 624;93 KB

-

Bang-bang Phase and Frequency Detector.png 1,489 × 615;121 KB

-

Bang-bang Phase Detector with “hold”.pdf 1,754 × 1,239;71 KB

-

Block diagram and noise equations 1-1.png 854 × 366;25 KB

-

Block diagram and noise equations 2-1.png 1,529 × 657;186 KB

-

Block diagram and noise equations 2-2.png 858 × 364;27 KB

-

Cascade of two CDRs with just different char frequency.png 748 × 320;18 KB

-

CDR based on 2nd PLL simple filter omega zeta vs G tau.png 794 × 350;23 KB

-

CDR basic architecture 2.png 531 × 190;23 KB

-

CDR PSDs and modulations.pdf 1,152 × 1,641;97 KB

-

CDR std 2nd PLL and variables.png 960 × 720;15 KB

-

CDR std 2nd PLL n variables.png 960 × 720;14 KB

-

CDR2 2 – 1 - actual shortcomings versus the ideal.png 627 × 439;60 KB

-

Char of a lin phase comp for different DT.pdf 1,614 × 454;34 KB

-

Char of a linear phase comp for different DT.png 1,385 × 391;113 KB

-

Charge pump and filter.png 1,034 × 443;33 KB

-

Charge pump.png 591 × 336;17 KB

-

ChargePumpPLLCircuit.svg 125 × 168;11 KB

-

Clock distribution.png 1,165 × 260;22 KB

-

Clock paths in the same domain.svg 830 × 380;112 KB

-

De Jitterer characteristics.png 785 × 313;19 KB

-

Definition of Phase Aligner..pdf 1,500 × 1,125;91 KB

-

Dejittering node.png 753 × 361;24 KB

-

Dejitterizing node Djv std.svg 697 × 348;99 KB

-

Delay locked loop, 0th order type 0 and 1st order type 1.png 935 × 596;72 KB

-

Digital PLL (block diagram).PNG 960 × 400;38 KB

-

Divide 4.png 304 × 160;5 KB

-

Divide 4.svg 512 × 269;5 KB

-

Dual modulus prescaler frequency synthesiser.svg 530 × 280;23 KB

-

Early-late gate PD w hold n table.pdf 1,754 × 1,239;61 KB

-

Elastic buffer operation.png 1,578 × 1,145;219 KB

-

Error signal 1 - 1.png 1,123 × 794;2.55 MB

-

Error signal 2 - 1.png 942 × 333;19 KB

-

Example of elastic buffer.png 430 × 273;12 KB

-

Eye sampling in PDs.png 1,360 × 830;73 KB

-

Faasilukk.png 592 × 317;25 KB

-

FILTRE1O.jpg 576 × 577;8 KB

-

FILTRE2O.jpg 1,194 × 832;17 KB

-

Filtro.png 1,108 × 821;25 KB

-

Freq synth.svg 530 × 220;20 KB

-

Gains and characteristics of bang-bang detectors.pdf 1,754 × 1,068;64 KB

-

Generic PLL diagram with OpAmp filter.png 887 × 600;31 KB

-

Hold in.svg 512 × 294;1.39 MB

-

Hold-in-expl2 4.svg 512 × 296;9 KB

-

Hold-in-expl2 5.svg 512 × 296;9 KB

-

I and Q instants and intervals.pdf 1,183 × 316;16 KB

-

I and Q instants and time intervals.png 966 × 195;28 KB

-

ITU-T G823 Fig 13 figure type.pdf 1,754 × 1,239;30 KB

-

Jitter tol 2-1 with slop. asympt.png 1,530 × 903;158 KB

-

Jitter tolerance also 2-1 and 2-2 zeta 0.5 omegan 3.14e6.png 1,054 × 454;33 KB

-

Jitter tolerance phase aligners.png 1,074 × 488;36 KB

-

Jitter transfer functions 1 1 , 2 1 , 2 2.pdf 1,754 × 1,239;60 KB

-

Jitter transfer functions 1 1 , 2 1 , 2 2.png 1,122 × 794;88 KB

-

Linear PLLs structures definitions.png 646 × 720;170 KB

-

Locked state pll 2.svg 512 × 648;3.68 MB

-

Locked state pll 3.svg 512 × 571;1.99 MB

-

Locked state pll.svg 512 × 599;3.68 MB

-

Loop filter diagram inside a 2nd order PLL.png 723 × 219;12 KB

-

Lowpass jitter filtering.pdf 1,239 × 1,754;95 KB

-

Model functions 1 - 0.pdf 1,754 × 1,239;69 KB

-

Model functions 1 - 1.pdf 1,754 × 1,239;72 KB

-

Models of the characteristic of bang-bang detectors.pdf 1,754 × 1,068;33 KB

-

Non-linear PLLs structures definitions.png 656 × 719;182 KB

-

Norm error functions 1 1 , 2 1 , 2 2.png 1,115 × 569;53 KB

-

Norm tolerance functions 1 1 , 2 1 , 2 2.png 916 × 443;29 KB

-

One wire only.png 789 × 348;18 KB

-

Oscillator spectrum.pdf 1,652 × 789;45 KB

-

Pass PFD.png 844 × 400;26 KB

-

Phase and Frequency Detector PFD.jpg 1,365 × 640;197 KB

-

Phase Detector using DETFFs and clocks I (lead) and Q (lag) at f 2.pdf 1,754 × 1,239;86 KB

-

Phase locked loop cs.svg 1,064 × 629;12 KB

-

Phase locked loop.svg 1,064 × 629;10 KB

-

Phase-locked loop.png 581 × 355;7 KB

-

Phasenrauschen(2).png 646 × 465;52 KB

-

PLL Blockschaltbild.png 493 × 273;2 KB

-

PLL F ARCHITECTURE.jpg 1,168 × 310;21 KB

-

PLL F BOUCLE FERMEE.jpg 587 × 720;20 KB

-

PLL F BOUCLE OUVERTE.jpg 582 × 724;21 KB

-

PLL F BRUIT DE PHASE.jpg 585 × 730;23 KB

-

PLL F FILTRE STABLE.jpg 586 × 729;22 KB

-

PLL F STABILITE.jpg 607 × 796;33 KB

-

PLL frequency synthesizer 2.svg 1,828 × 1,160;40 KB

-

PLL generic inline optional N.png 900 × 200;17 KB

-

PLL generic inline optional N.svg 1,026 × 186;8 KB

-

PLL generic inline.svg 900 × 200;11 KB

-

PLL generic it.svg 650 × 245;11 KB

-

PLL generic.svg 633 × 239;7 KB

-

PLL usage it.svg 720 × 190;10 KB

-

PLL usage.svg 521 × 114;20 KB

-

PLL,generic.png 629 × 239;4 KB

-

PLL,usage.png 800 × 242;14 KB

-

PLL-Block.PNG 398 × 90;3 KB

-

PLL-DetectorFase-JK.png 374 × 355;10 KB

-

PLL-detectorFase-XOR.png 392 × 372;11 KB

-

PLL-detectorFrecFase.png 254 × 209;8 KB

-

PLL-phase-model-01.jpg 1,642 × 526;177 KB

-

Pll.png 768 × 288;3 KB

-

PLL1 de.svg 400 × 205;18 KB

-

PLL1 it.svg 400 × 205;16 KB

-

PLL1.PNG 398 × 213;6 KB

-

PLL1.png 549 × 254;10 KB

-

PLL2.PNG 447 × 100;3 KB

-

Ring Oscill DJv pdf IS.svg 563 × 506;29 KB

-

Sagedussünt.png 596 × 336;18 KB

-

Schema PLL.png 540 × 282;8 KB

-

Schematic of PLL 1st order.png 571 × 199;9 KB

-

Schematic of PLL 2nd order.png 498 × 368;18 KB

-

Schematic of simulated PLL Rev. 2.png 960 × 720;50 KB

-

Schematic of simulated PLL.png 908 × 613;34 KB

-

Set diagram of CDRs and PLLs.png 493 × 423;60 KB

-

SimplePLL.png 415 × 169;6 KB

-

SimplePLL.svg 434 × 166;11 KB

-

Single Zero Filter.png 1,155 × 803;76 KB

-

Static gain of comparators.png 1,385 × 671;132 KB

-

StatiPFD.png 1,123 × 397;1.28 MB

-

Step response of the single zero filter.pdf 1,754 × 1,239;16 KB

-

Structures definitions and their fit.pdf 1,500 × 1,125;56 KB

-

Structures.png 1,197 × 721;237 KB

-

The Architecture of the PLL of a CDR is defined by two numbers.pdf 1,500 × 1,125;40 KB

-

The classic (Hogge) phase comparator.png 977 × 461;78 KB

-

The LOS unlocks the CDR.png 610 × 477;24 KB

-

Tol & Transf of CDRs in a de-jitterizer.png 673 × 257;32 KB

-

Tol & Transf of CDRs in a de-jitterizer.svg 673 × 257;34 KB

-

Tol vectors at 0.2.png 1,090 × 1,144;107 KB

-

Tol vectors at 0.8.png 1,090 × 1,144;99 KB