Category:Digital circuit diagrams

Jump to navigation

Jump to search

Media in category "Digital circuit diagrams"

The following 103 files are in this category, out of 103 total.

-

2bsuml.jpg 770 × 427; 52 KB

-

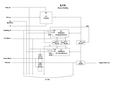

3B ALU 2T-1T.JPG 820 × 560; 91 KB

-

3bsumm3l.jpg 350 × 356; 20 KB

-

3bsumsd.jpg 962 × 356; 74 KB

-

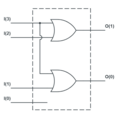

4-to-2encoder.svg 396 × 332; 5 KB

-

4to2 Simple Encoder.png 652 × 596; 26 KB

-

4to2SimpleEncoder.png 571 × 581; 27 KB

-

8-to-3encoder.svg 428 × 460; 13 KB

-

8to3SimpleEncoder.png 716 × 820; 47 KB

-

Accasoc GRAFCET.PNG 445 × 280; 6 KB

-

All pass interpolator.svg 1,280 × 720; 12 KB

-

ARMSoCBlockDiagram.svg 500 × 600; 89 KB

-

AsynchSynch.gif 1,920 × 1,409; 47 KB

-

Automat moore'a uklad.png 634 × 570; 8 KB

-

Automate de Mealy.png 491 × 436; 14 KB

-

Automate de Moore et de Mealy.png 1,015 × 779; 36 KB

-

Automate de Moore. 01.png 733 × 356; 17 KB

-

Balanced path delay2.JPG 360 × 204; 23 KB

-

Bus holder circuit.svg 181 × 216; 9 KB

-

CI-grind.PNG 156 × 96; 1 KB

-

Circuit séquentiel synchrone.png 609 × 326; 12 KB

-

Circuito combinacional.svg 228 × 88; 7 KB

-

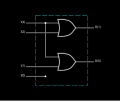

Combinational circuit NAND gates.svg 531 × 283; 10 KB

-

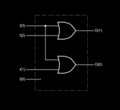

Common term multifunction.svg 531 × 283; 10 KB

-

Conception d'un circuit à partir de maxterms.jpg 913 × 337; 70 KB

-

Conception d'un circuit à partir de minterms.jpg 995 × 400; 83 KB

-

CurrentSwitchLogicPlain.svg 1,052 × 744; 113 KB

-

Delay Analyze Cuircuit Bad 000.svg 450 × 375; 16 KB

-

Delay Analyze Cuircuit Bad 001.svg 450 × 375; 22 KB

-

Delay Analyze Cuircuit Bad 004.svg 450 × 375; 22 KB

-

Delay Analyze Cuircuit Bad 005.svg 450 × 375; 22 KB

-

Delay Analyze Cuircuit Bad 006.svg 450 × 375; 22 KB

-

Delay Analyze Cuircuit Bad 008.svg 450 × 375; 22 KB

-

Delay Analyze Cuircuit Clock Distribution.svg 450 × 375; 12 KB

-

Delay Analyze Cuircuit Good 004.svg 450 × 375; 21 KB

-

Delay Analyze Cuircuit Good 007.svg 450 × 375; 22 KB

-

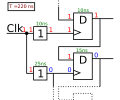

Delay Analyze Cuircuit Shift Register.svg 450 × 375; 12 KB

-

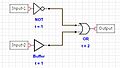

Digital circuit.JPG 253 × 123; 12 KB

-

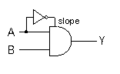

DigitalInverter.png 386 × 382; 6 KB

-

DigitalnaKola2.jpg 333 × 173; 14 KB

-

Direcc GRAFCET.PNG 585 × 176; 5 KB

-

Electronics TTL NOT Gate.PNG 254 × 219; 2 KB

-

ExampleExecutionUnit.svg 1,000 × 1,000; 35 KB

-

ExecutionUnitForMultiplication.svg 1,000 × 1,000; 56 KB

-

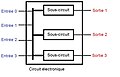

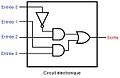

Exemple d'un circuit électronique à une seule sortie.jpg 582 × 379; 19 KB

-

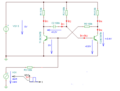

Fonctionnement d'un comparateur avec une constante.jpg 890 × 405; 43 KB

-

Funcion logica NO-O-EX.PNG 482 × 142; 4 KB

-

Funcion logica NO-O.PNG 482 × 142; 3 KB

-

Funcion logica NO-Y.PNG 482 × 142; 3 KB

-

Funcion logica NO.PNG 482 × 142; 3 KB

-

Funcion logica O-EX.PNG 482 × 142; 4 KB

-

Funcion logica SI.PNG 482 × 142; 3 KB

-

Funcion logica Y.PNG 482 × 142; 3 KB

-

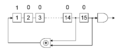

Gestion des débordements d'entiers.png 777 × 314; 30 KB

-

GRAFCET condicional.PNG 406 × 146; 3 KB

-

GRAFCET ejemplo montacargas.PNG 534 × 189; 5 KB

-

IBM 608 Logic Gates.jpg 1,160 × 544; 77 KB

-

Karnaugh map KV Lampe.svg 950 × 500; 11 KB

-

Karnaugh map KV Race Hazard Gatter 1a.svg 1,200 × 800; 16 KB

-

Karnaugh map KV Race Hazard Gatter 2a.svg 1,200 × 800; 16 KB

-

Karnaugh map KV Race Hazard Gatter 3a.svg 1,200 × 800; 16 KB

-

Karnaugh map KV Race Hazard Gatter 4a.svg 1,200 × 800; 16 KB

-

Karnaugh map KV Race Hazard Gatter 5b.svg 1,200 × 800; 19 KB

-

KOL Grid Data.PNG 800 × 500; 13 KB

-

KOL Memory 2.PNG 1,100 × 800; 34 KB

-

KOL Memory Block.PNG 1,200 × 600; 22 KB

-

Linear interpolator.svg 1,280 × 720; 9 KB

-

Mfrey Cross Connected T.svg 120 × 120; 3 KB

-

Mfrey Cross Connected.svg 120 × 120; 4 KB

-

Mfrey Cross explicit not Connected.svg 120 × 120; 3 KB

-

Mfrey Cross not Connected.svg 120 × 120; 3 KB

-

MFrey EQU Discret.svg 240 × 120; 22 KB

-

MFrey Latch Edge Reset.svg 270 × 670; 24 KB

-

MFrey Latch Edge.svg 270 × 670; 24 KB

-

MFrey Latch State.svg 270 × 670; 24 KB

-

Mfrey T explicit Connected.svg 120 × 120; 4 KB

-

Mfrey T implicit Connected.svg 120 × 120; 3 KB

-

MFrey XOR Discret.svg 240 × 120; 22 KB

-

Monostabile Kippstufe - Analyse 040.PNG 587 × 446; 16 KB

-

Monostabile Kippstufe - Analyse 043.PNG 587 × 446; 15 KB

-

Monostabile Kippstufe - Analyse 044.PNG 587 × 446; 15 KB

-

Pamiec ROM.svg 350 × 310; 51 KB

-

PRBS 15 generator.png 1,955 × 873; 8 KB

-

Race condition.svg 262 × 349; 17 KB

-

RAM.png 320 × 256; 4 KB

-

S-Net-Moore.svg 559 × 251; 4 KB

-

Schaltnetz mit hazard.png 400 × 192; 8 KB

-

Schaltnetz ohne hazard.png 400 × 192; 9 KB

-

Secsimul GRAFCET.PNG 545 × 234; 6 KB

-

Sequential circuits.jpg 1,275 × 1,650; 67 KB

-

Synchronous Sequential Circuits.jpg 1,275 × 1,650; 59 KB

-

Taks Claculate Delay 001.svg 340 × 290; 39 KB

-

Taks Claculate Delay 002.svg 340 × 290; 40 KB

-

Taks Claculate Delay 003.svg 340 × 290; 40 KB

-

Taks Claculate Delay.svg 340 × 290; 28 KB

-

Type circuit.jpg 593 × 441; 45 KB

-

WillWareBluetoothBitBangSchematic.png 506 × 422; 10 KB

-

XOR with AOI logic in CMOS.svg 272 × 306; 28 KB

-

Zirkuitua.jpg 1,704 × 899; 527 KB

-

Снимок модели 3B ALU 2T-1T.JPG 660 × 465; 68 KB