Category:RAM microarchitecture

Jump to navigation

Jump to search

Media in category "RAM microarchitecture"

The following 60 files are in this category, out of 60 total.

-

Accès mémoires avec pipeline.jpg 864 × 189; 18 KB

-

Accès mémoires sans pipeline.jpg 865 × 84; 13 KB

-

Adressage par bloc.png 453 × 347; 2 KB

-

Adressage par coïncidence stricte - intérieur de la mémoire.png 685 × 419; 15 KB

-

Adressage par coïncidence stricte.png 480 × 363; 9 KB

-

Adressage par coïncidence.png 480 × 331; 6 KB

-

Adresse mémoire d'une mémoire entrelacée.png 725 × 124; 2 KB

-

Amplificateur de lecture à bascule, avec transistors d'activation.png 1,099 × 548; 15 KB

-

Amplificateur de lecture à bascule, version détaillée.png 1,003 × 548; 14 KB

-

Arrangement horizontal.jpg 695 × 414; 38 KB

-

Arrangement vertical.jpg 867 × 248; 22 KB

-

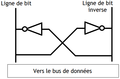

Bitlines croisées.png 422 × 502; 6 KB

-

Bitlines différentielles.png 422 × 523; 8 KB

-

Circuit d'interface entre contrôleur mémoire et cellule mémoire.png 506 × 373; 10 KB

-

Circuits d'une mémoire interleaved par rafale.png 634 × 307; 4 KB

-

Circuits de précharge.png 801 × 480; 15 KB

-

Divided word line.png 523 × 347; 2 KB

-

DRAM Adressdekodierung.png 989 × 838; 23 KB

-

DRAM bus read voltage reference.png 1,282 × 822; 39 KB

-

DRAM Rank.svg 1,355 × 625; 38 KB

-

DRAM Ranks.svg 1,433 × 1,000; 48 KB

-

DRAM.svg 400 × 400; 3 KB

-

Fonctionnement très simplifié de l'amplificateur à verrou.png 737 × 481; 17 KB

-

HMCLogicArchitecture.png 676 × 439; 56 KB

-

L'intérieur d'une FPM.png 833 × 546; 23 KB

-

Latch-type sense amplifier.png 499 × 328; 7 KB

-

Ligne de bit repliée.png 462 × 455; 6 KB

-

Lignes de bit repliées.png 422 × 523; 6 KB

-

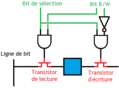

Lignes de bits pour les cellules mémoires double port.png 421 × 521; 9 KB

-

Macro2Mbit.PNG 534 × 504; 13 KB

-

Macro4Mbit.png 382 × 513; 2 KB

-

Modifications du contrôleur mémoire liées aux accès en rafale.png 833 × 592; 25 KB

-

Mémoire avec double envoi.png 751 × 230; 9 KB

-

Mémoire à row buffer. 01.png 630 × 491; 15 KB

-

Mémoire à row buffer. 02.png 765 × 564; 21 KB

-

Mémoire à tampon de ligne.png 660 × 413; 12 KB

-

Optimisations du plan mémoire pour réduire la taille des bitlines.png 1,013 × 368; 10 KB

-

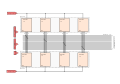

Plan mémoire d'une mémoire bit-adressable.png 520 × 547; 12 KB

-

Plan mémoire d'une SRAM double port.png 718 × 547; 14 KB

-

Plan mémoire d'une SRAM simple port.png 584 × 430; 8 KB

-

Plan mémoire simplifié d'une mémoire bit-adressable.png 388 × 547; 6 KB

-

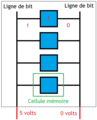

Plan mémoire, avec les bitlines.png 460 × 370; 4 KB

-

Principe d'un plan mémoire linéaire. 01.png 460 × 370; 5 KB

-

Rafraichissement mémoire automatique.png 833 × 590; 25 KB

-

RAM memory intenrals.png 784 × 339; 13 KB

-

Regfile array.png 202 × 217; 2 KB

-

Row hammer.svg 400 × 400; 5 KB

-

Répartition des adresses dans une mémoire interleaved.png 426 × 543; 3 KB

-

Répartition des adresses sans entrelacement.png 556 × 543; 4 KB

-

Sense Amp position.jpg 400 × 681; 31 KB

-

Signal row line.png 607 × 204; 5 KB

-

Square array of mosfet cells read.png 630 × 930; 5 KB

-

Square array of mosfet cells read.svg 630 × 930; 6 KB

-

Square array of mosfet cells write.png 640 × 930; 6 KB

-

Struttura interna RAM.png 1,066 × 442; 9 KB

-

Td6bfig1.png 631 × 319; 32 KB

-

Td6bfig3.png 722 × 270; 32 KB