Category:Semiconductor devices fabrication

Jump to navigation

Jump to search

manufacturing process used to create integrated circuits | |||||

| Upload media | |||||

| Instance of | |||||

|---|---|---|---|---|---|

| Subclass of |

| ||||

| Location | semiconductor fabrication plant | ||||

| |||||

Subcategories

This category has the following 21 subcategories, out of 21 total.

B

C

- CMOS manufacture (13 F)

D

E

F

I

L

M

N

P

S

T

- Thermosonic bonding (6 F)

- Transistor dies (160 F)

W

Media in category "Semiconductor devices fabrication"

The following 64 files are in this category, out of 64 total.

-

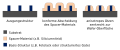

14 nm half-pitch multipatterning.png 910 × 375; 23 KB

-

14 nm half-pitch multipatterning.svg 743 × 337; 49 KB

-

4-fach-NAND-C10.JPG 967 × 1,206; 1.6 MB

-

7 nm litho options.png 859 × 582; 410 KB

-

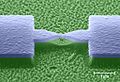

Alu bridge.jpg 1,020 × 694; 214 KB

-

Anti-spacer Double patterning.png 815 × 593; 16 KB

-

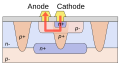

APD structure.svg 750 × 678; 27 KB

-

APD with Superlattice.svg 681 × 633; 8 KB

-

APD.png 400 × 290; 21 KB

-

Ballbond-trand.png 2,331 × 1,197; 148 KB

-

Bell telephone magazine (1922) (14569544079).jpg 2,064 × 1,684; 1.34 MB

-

Bivar-logo.png 213 × 60; 3 KB

-

Buried zener structure-en.svg 521 × 283; 5 KB

-

Buried zener structure.svg 521 × 283; 16 KB

-

Buried zener vs npn epi.svg 521 × 616; 26 KB

-

Centrotherm diffusion furnace at LAAS 0489.jpg 2,592 × 3,872; 3.85 MB

-

Centrotherm diffusion furnace at LAAS 0491.jpg 2,592 × 3,872; 3.78 MB

-

Centrotherm diffusion furnace at LAAS 0493.jpg 2,592 × 3,872; 4 MB

-

Centrotherm diffusion furnaces at LAAS 0481.jpg 2,592 × 3,872; 4.22 MB

-

Comparison semiconductor process nodes.svg 990 × 765; 72 KB

-

Dicing blade.jpg 578 × 443; 87 KB

-

Diferencia estructura.PNG 552 × 240; 41 KB

-

DRAM burried capacitor configuration.svg 800 × 600; 4 KB

-

DRAM self-aligned storage node locations.png 706 × 550; 52 KB

-

DRAM trench configuration 2.svg 512 × 512; 4 KB

-

DRAM trench structure configuration1 1.svg 512 × 512; 6 KB

-

DRAM trench structure configuration1.svg 800 × 600; 6 KB

-

Field-induced MRAM schematic ja.png 5,464 × 4,672; 132 KB

-

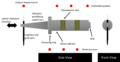

GeS CVD setup.png 1,254 × 607; 89 KB

-

GST CVD setup.png 467 × 233; 55 KB

-

GST CVD setup.tif 1,074 × 538; 220 KB

-

Illustration of C-V measurement.gif 322 × 308; 93 KB

-

KO fig21 applications Corelv11.png 1,748 × 1,799; 483 KB

-

Laser diode with case cut away.jpg 512 × 437; 118 KB

-

LELE challenge.png 472 × 353; 5 KB

-

Lift-off (microtechnology) process.svg 512 × 664; 31 KB

-

Lift-off-Verfahren (Fehlerbilder).svg 1,100 × 600; 44 KB

-

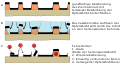

Lift-off-Verfahren (Halbleitertechnik).svg 1,024 × 756; 41 KB

-

Line cut location offset.png 417 × 442; 6 KB

-

Main applications of ALD.png 1,692 × 1,718; 317 KB

-

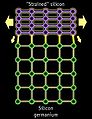

Microprocessore silicio germano.jpg 250 × 324; 21 KB

-

Molecular Beam Epitaxy.png 1,400 × 739; 153 KB

-

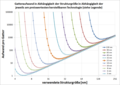

Moore Kosten.png 943 × 665; 36 KB

-

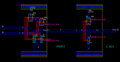

OR2 layout.PNG 678 × 348; 19 KB

-

Organic transistor Greek.png 415 × 211; 95 KB

-

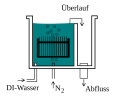

Overflow.svg 1,000 × 800; 24 KB

-

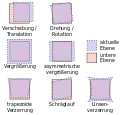

Overlay - typical model terms DE.svg 617 × 591; 16 KB

-

Piranha solution.png 864 × 1,536; 1.55 MB

-

SADP challenge.png 504 × 497; 8 KB

-

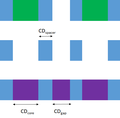

SADP then SATP.png 668 × 253; 8 KB

-

Salle blanche ensim.jpg 4,256 × 2,832; 5.61 MB

-

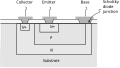

Schottky-Transistor-Side.svg 364 × 204; 22 KB

-

Self-aligned silicidation.svg 1,990 × 692; 52 KB

-

SemiconductorProcessSize.png 1,440 × 852; 48 KB

-

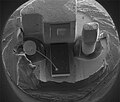

Siliconchip by shapeshifter.png 1,276 × 891; 1.83 MB

-

Spacer formation (DE).svg 875 × 361; 14 KB

-

Spacer Patterning.JPG 393 × 576; 19 KB

-

Spacer trimming.png 1,157 × 484; 17 KB

-

The entrance of 3S Silicon Tech., Inc.jpg 898 × 783; 386 KB

-

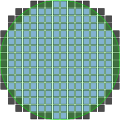

Trilogy WSI Wafer.png 1,920 × 1,920; 7.45 MB

-

Two-bar challenge.png 601 × 351; 8 KB

-

Wafermap showing fully and partially patterned dies.svg 657 × 657; 103 KB

-

Worldwide Semiconductor Sales in Billion US-Dollar GERMAN.jpg 621 × 327; 27 KB